一、前言

RSC6218A是一款可以满足4项标准的优秀产品:①2024年8月1日要实施的《建筑照明设计标准》GBT0034-2024;②2024年07月01日起实施的《电磁兼容限值 第1部分:谐波电流发射限值(设备每相输入电流≤16A)》GB17625.1-2022;③已实施的教育照明标准:GB/T 36876-2018;④已实施的欧盟新版ERP EU2019/2020;本篇分享的是应用RSC6218A设计18W高效率电源驱动的案例。

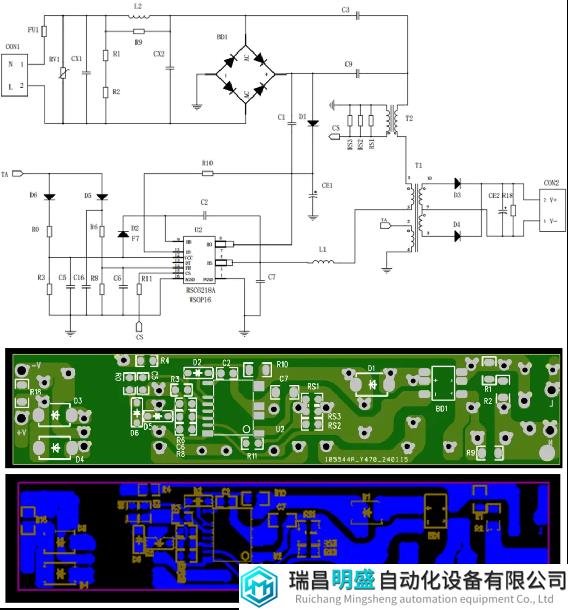

二、RSC6218A 18W案例

二、RSC6218A 18W案例

开关电源的开关特性会使电源的MOS与变压器产生电磁兼容方面的干扰,优秀的PCB Layout可以解决电磁兼容问题,同时也可有效避免干扰源的扩大;如图结合实例说明RSC6218A系列LLC谐振电源方案PCB的设计要点,提升LLC谐振方案的稳定性。

1、严格遵循功率“地”、信号“地”分离的原则,如图示例中CS电阻的地单点连到高压电解CE1的负端处;芯片地是重点,LAYOUT时注意:①芯片的AGND,FB下偏电阻的“地”先回到VCC的电容C5“地”,然后再回到CE1的负端处;②芯片的PGND单点连到高压电解CE1的负端处;

2、减小主功率环路的面积,包括谐振腔回路、开关功率回路、负载电流回路,可有效减少干扰源的扩大;如图示例中加粗线的部分走线铜箔;

3、自举升压回路注意点,自举二极管与电容的结点靠近PIN10之HB脚,可避免外来干扰引入,影响系统的稳态工作;

4、FB引脚的上偏与下偏采样电阻和滤波电容的结点一定要靠近芯片PIN14之FB脚,否则会影响OVP点以及可拉载的电压点,影响系统的稳定性;

5、CS引脚的取样电阻R11应靠近芯片PIN15之CS脚,并且要远离存在较高di/dt的走线,减少造成恒流点不稳定因素;

6、在使用散热器时,散热器上会有高频电流流过,所以散热器应就近接“地”,这样可减少干扰源的扩大;

7、芯片背面PCB正上方尽量不要放置与芯片的“地”存在较高动态电压差的器件,例如变压器、卧躺式且大平面紧贴PCB朝下的TO-220封装MOSFET;

8、谐振电感与电流互感器在线路中放置的位置可以调整,LAYOUT时可以根据实际布线需要放置,方便走线取样与产品稳定性。

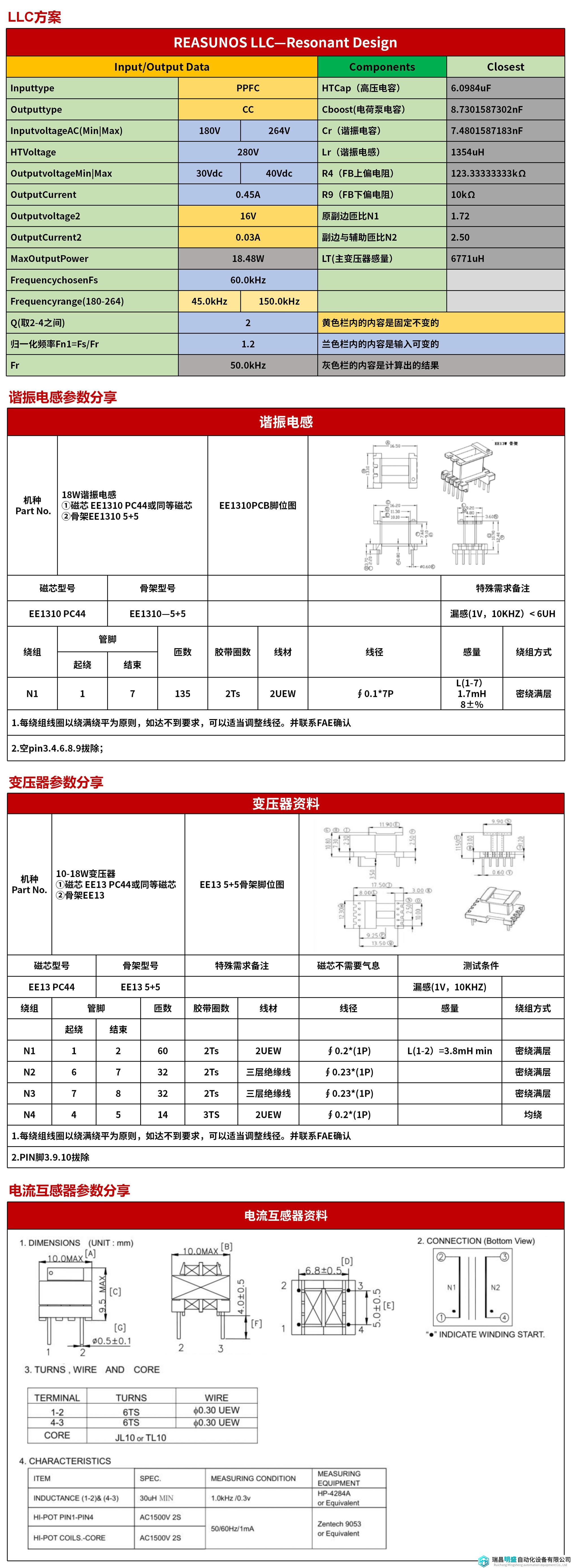

三、关键器件的设计指导与选料规格

简洁可靠的理论指导,优化关键器件的范围与选料规格,让工程师朋友们设计LLC方案变得有理有据,通俗易懂,轻松应对客户开案的需求。

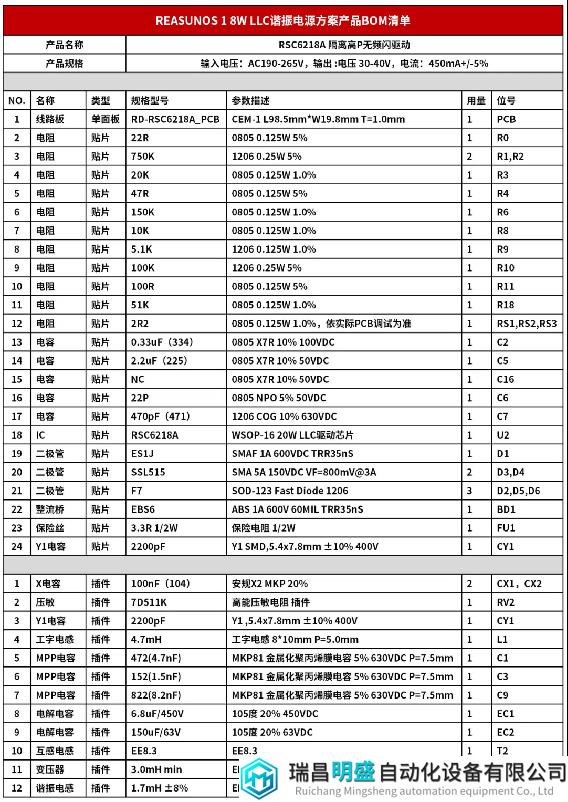

四、实际物料清单BOM分享

瑞森半导体提供完善的设计参考资料与广大工程师朋友进行分享,用心做好芯片,用心做好服务,愿与客户共成长,实现共赢的目标。